Micron Know-how Talks about NAND as nicely, 232-layer 3D NAND flash technology inbound

In a keynote address, top vendor Micron Technology (Micron) talked about scaling techniques for 3D NAND flash technological know-how. Stacking memory cells perpendicular to the surface area of the silicon wafer is the most successful approach to enhancing the density and potential of 3D NAND flash.

Micron has designed and mass-made 176-layer 3D NAND flash with a enormous variety of stacked cells. Additionally, on May perhaps 12, 2022, just prior to IMW 2022, the business mentioned to investors during a briefing session that it has developed 232-layer 3D NAND flash technologies. Primarily based on a straightforward calculation, the memory density is 1.32 periods that of 176 layers. The trader briefing slide depicted a TLC (3little bit / mobile) system 1Tbit die photograph. In addition, though not revealed in the IMW 2022 publication, the investor briefing slide was exhibited during the keynote handle.

As opposed to stacking in the vertical direction (Z direction), densification is slower parallel to the silicon wafer area (horizontal course or XY path). Even so, makes an attempt are becoming undertaken to enhance the density by escalating the distance amongst sacrificial etching grooves. In the past, grooves were equipped for each individual of the four channels (pillars), however for every of the 9 channels, this was altered. Consequently, the density is improved by 14 p.c. Nonetheless, if the variety is larger than nine, the groove spacing can be widened with no a important boost in density.

An hard work to enhance the density by growing the interval concerning sacrificial etching groove insertions. In accordance to a report launched by Micron Engineering in IMW 2022, there are also attempts to lessen the channel width and channel pitch in order to increase the density. This approach necessitates enhancements in lithography and etching, although the density boost is negligible. Rising the variety of memory cells stacked vertically complicates channel etching. Thus, an energy is built to limit the peak development by thinning just about every layer (tier). Nevertheless, thinning the tier raises the parasitic resistance and capacitance of the term line, which slows down generate and go through operations. Even additional hazardous, if it is designed much too slender, the electrical interference involving neighboring cells will be way too good to ignore.

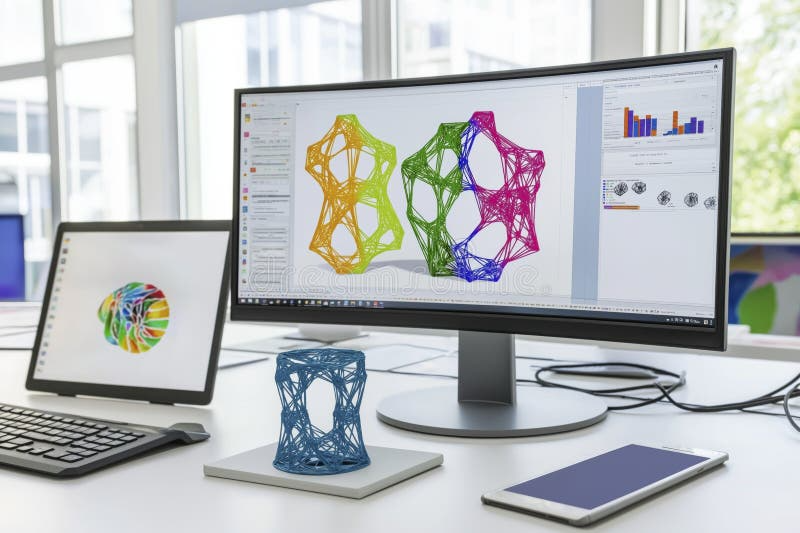

Versions in 2D NAND flash and 3D NAND flash channel tier pitch (TP) and channel width (W). From a analyze published in IMW 2022 by Micron Know-how (Paper No. 1.1) In addition, Micron supplied possibilities to raise enter and output speeds. In 3D NAND flash, techniques for raising storage density by monolithically stacking CMOS logic peripheral circuits and memory cell arrays are getting recognition. With this process, however, CMOS peripheral circuits are uncovered to the memory mobile array procedure (superior temperature processing) and deteriorate, which may possibly impede the improvement of functioning speed. As a result, a technique has been developed in which a CMOS peripheral circuit is made on yet another silicon wafer and bonded to a memory mobile array wafer.

Craze of input/output velocity enhancement for 3D NAND memory. From a review released in IMW 2022 by Micron Technology (Paper No. 1.1) The engineering necessary to understand 3D NAND flash will become progressively difficult, but its boundaries have not nonetheless been identified. Until more detect, we can anticipate an boost in memory density.